Acaba de salir hace 5 minutos (esta vez nos hemos adelantado a gaf xd) éste documento en la web que filtró todas las especificaciones de Xbox One y PS4 a primeros de año.

Anuncian que van a sacar más información. Esta con la traducción de google y ligeramente revisado, después de comer lo vuelvo a mirar para que se entienda un poco mejor, aunque no es sencillo.

http://www.vgleaks.com/playstation-4-in ... echnology/PlayStation 4 incluye tecnología HUMAHa habido mucha controversia sobre este asunto en los últimos días, pero vamos a tratar de aclarar que Playstation 4 soporta la tecnología Huma o por lo menos que implementa una primera revisión de la misma. Tenemos que recordar que AMD no ha lanzado productos con tecnología Huma todavía , por lo que es difícil comparar con algo en el mercado. Además, hay especificaciones están terminados todavía se resuelven, por lo tanto PS4 aplicación puede diferir un poco de las implementaciones con Huma finalizado.

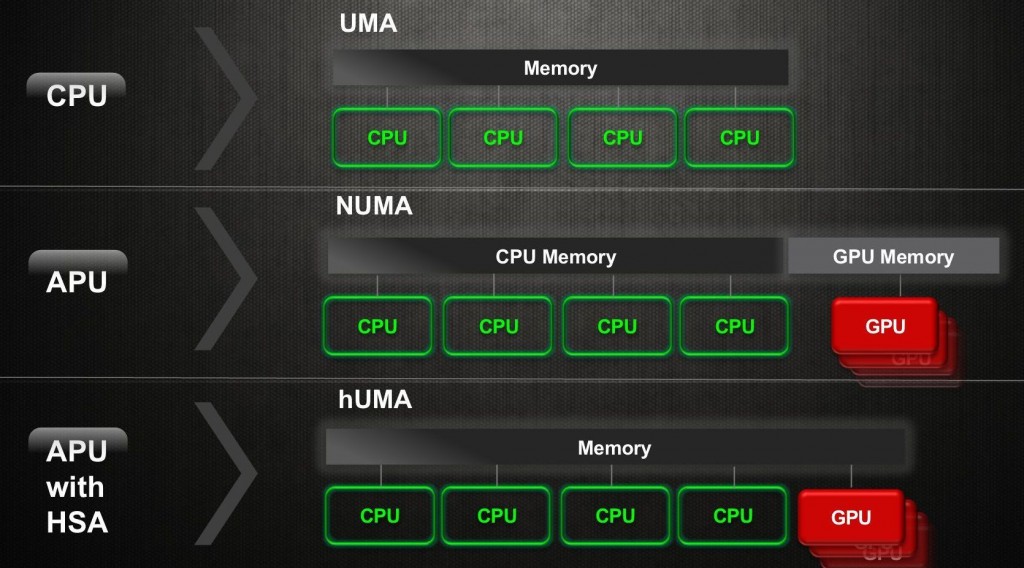

Pero ante todo, ¿qué es Huma ? Huma es el acrónimo de Uniform Memory Access heterogénea . En el caso de Huma ambos procesadores ya no distinguen entre la CPU y la GPU áreas de memoria. Tal vez esta imagen podría explicar el concepto de una manera sencilla:

Si usted desea aprender más acerca de esta tecnología, este artículo se explica cómo funciona Huma.

PS4 tiene mejoras en la arquitectura de memoria que ningún otro producto "menor" tiene como Marcos Cerny señaló en distintas entrevistas. Vamos a tratar de mostrar las nuevas piezas en PS4 componentes en las páginas siguientes.

Tenemos que poner nuestro diagrama sobre la arquitectura de memoria de PS4 para explicar cómo funciona.

Cartografía de la memoria en Liverpool

- Direcciones son de 40 bits. Este tamaño permite que las páginas de memoria asignadas tanto en CPU y GPU tengan la misma dirección virtual

- Páginas de la memoria son establecidas libremente por la aplicación

- Páginas de memoria no tienen que ser a la vez asignada en la CPU y la GPU

Si sólo la CPU va a utilizar, la GPU no tiene por qué lo han asignado

Si sólo el GPU va a utilizar, se accederá a través de Ajo

- Si la CPU y la GPU accederán a la página de memoria, la determinación debe hacerse si la GPU debe acceder a ella a través de cebolla o ajo

Si la GPU necesita gran ancho de banda, la página debe ser accesible a través de Ajo, la CPU tendrá que acceder a él memoria, no en caché

Si la CPU tiene acceso frecuente a la página, debe ser asignada como memoria caché de la CPU, la GPU tendrá que acceder a ella a través de cebolla.

Cinco Tipo de Buffers

- Buffers de memoria del sistema que utiliza la GPU etiquetados como uno de los cinco tipos de memoria

- Los tres primeros tipos tienen acceso a la CPU muy limitado, el acceso principal es por la GPU

- Sólo lectura (RO)

Un buffer "RO" es la memoria que se lee por CU de pero nunca escrito a ellos, por ejemplo, una textura o una mesa vértice

El acceso a memorias intermedias de ósmosis inversa nunca puede causar cachés L1 a pierden coherencia entre sí, ya que es escribir las operaciones que causan problemas de coherencia.

- Privada (PV)

Un buffer "PV" es la memoria privada leer y escribir mediante un solo ThreadGroup, por ejemplo, una memoria intermedia temporal.

El acceso a los búferes de PV nunca pueden causar cachés L1 a pierden coherencia, ya que es escribe en compartidos áreas de memoria que causan los problemas

- GPU coherente (GC)

Un buffer "GC" es la memoria leer y escribir mediante el CU de como resultado de las llamadas dibujar o despachos, por ejemplo, salidas de vertex shaders / que luego son leídos por los shaders de geometría. Topes de profundidad y destinos de representación no son de memoria GC, ya que no se escriben en la CU, pero por hardware dedicado en el DB y CBs.

Como escribe se permite buffers GC, el acceso a ellos puede causar cachés L1 de perder la coherencia con los demás

- Los dos últimos tipos son accesibles por la CPU y GPU

- El sistema coherente (SC)

Un buffer "SC" es la memoria leídos y escritos por tanto a la CPU y la GPU, por ejemplo, la CPU lee la estructura de la GPU, o estructuras utilizadas para la comunicación CPU-GPU

Buffers SC presentan los mayores problemas de coherencia. No sólo se puede cachés L1 pierden coherencia con otras, pero ambos L1 y L2 pueden perder la coherencia con la memoria del sistema y los cachés de CPU.

- Uncached (UC)

Un buffer "UC" es la memoria que se lee y se escribe en la CPU y GPU, al igual que la SC fue

Buffers UC no se almacenan en caché en el GPU L1 o L2, por lo que no presentan problemas de coherencia

UC accede a utilizar la nueva cebolla + bus, un bus de ancho de banda limitado similar al bus Cebolla

Accesos UC pueden tener importantes ineficiencias debido a repetidas lecturas de la misma línea o actualizaciones incrementales de las líneas

- Los tres primeros tipos (RO, PV, GC) pueden también tener acceso a la CPU, pero hay que tener cuidado. Por ejemplo, cuando se copia una textura a una nueva ubicación

La CPU puede escribir los datos de la textura de una manera no está en caché, a continuación, eliminar manualmente los caches GPU. La GPU puede, posteriormente, acceder a la textura como la memoria RO través de Ajo a alta velocidad

Dos peligros se evitan aquí. A medida que la CPU worte los datos de textura utilizando Uncached escribe, no quedan datos en la caché de la CPU y la GPU es de uso gratuito ajo en vez de cebolla. Como la CPU enrojeció las cachés GPU después de la configuración de la textura, no hay posibilidad de datos obsoletos en la GPU L1 y L2.

Seguimiento del tipo de accesos a memoria

- Accesos a memoria se hacen a través de V y T # # definiciones que contienen la dirección de base y otros parámetros de la memoria intermedia o la textura

- Tres bits se han añadido a V y T # # para especificar el tipo de memoria

- Y poco más se ha añadido a las etiquetas L1

Se establece si la línea se carga desde la memoria de GC o SC (en oposición a la memoria RO o PV)

Un nuevo tipo de L1 basada en paquetes invalidar se ha añadido que sólo invalida la líneas de GC y SC

Una estrategia simple es para código de aplicaciones para usar esta invalidación ante cualquier llamada empate o despacho que tiene acceso a GC o tampones SC

- Bit adicional se ha añadido a la L2 etiquetas

Indica si la línea se carga desde la memoria SC

Un nuevo L2 invalida apenas de las líneas SC se ha añadido

Un nuevo L2 reescritura de algo las líneas SC ha añadido. Estos dos están basadas en paquetes.

Una estrategia simple es para código de aplicaciones para utilizar la L2 invalida ante cualquier llamada empate o despacho que utiliza amortiguadores SC, y el uso de la L2 reescritura después de cualquier llamada empate o despacho que utiliza buffers SC

La combinación de estas características permite la adquisición eficiente y liberación de buffers de llamadas empate y despachos

Ejemplo simple:

- Vamos a tomar el caso en la mayor parte de la GPU está siendo utilizado para los gráficos (vertex shaders, shaders de pixel y así sucesivamente)

- Por otra parte, supongamos que tenemos un despacho cálculo asincrónico que utiliza una memoria tampón SC para:

Despacho entradas con son creados por la CPU y leído por el GPU

Despacho salidas, que se crean por la GPU y leídos por la CPU

- La GPU puede:

1) Adquirir el buffer SC mediante la realización de una L1 invalida (GC y SC) y L2 invalida (sólo las líneas SC). Esto elimina la posibilidad de datos obsoletos en las cachés. Cualquier dirección SC encontró irán adecuadamente offchip (en la memoria del sistema o caches de CPU) para recuperar los datos.

2) Ejecutar el sombreado cálculo

3) Suelte el buffer SC realizando una reescritura L2 (sólo líneas SC). Esto escribe todos los bytes sucios de nuevo a la memoria del sistema en la CPU pueda verlos

- El procesamiento de gráficos está mucho menos afectado por esta estrategia

Por R10XX, la L2 completo se inundó, por lo que los datos de uso de los shaders gráficos (por ejemplo, las texturas actuales) tendrían que ser recargada

El Liverpool, que los datos RO permanece en el lugar - como lo hace los datos de PV y GC

Esta información técnica puede ser un poco abrumador y confundir, por lo tanto, vamos a divulgar más información y ejemplos de uso de esta arquitectura en un nuevo artículo de esta semana .