dXoco escribió:Creo que se deberia revisar porque se banea a un usuario. Infracciones? Lo siento pero no las veo.

Es un hilo de xbox one y se le banea por defenderla?

Yo no entiendo nada

![facepalm [facepalm]](/images/smilies/facepalm.gif) , parece que aquí no interesa nada bueno sobre esta consola

, parece que aquí no interesa nada bueno sobre esta consola dXoco escribió:Creo que se deberia revisar porque se banea a un usuario. Infracciones? Lo siento pero no las veo.

Es un hilo de xbox one y se le banea por defenderla?

Yo no entiendo nada

Chifrinillo escribió:Bueno, volviendo al topic del hilo.

Están hablando de que en el X D K, hablan por un lado de los SC y por otro de los CU y que tienen una descripción radicalmente distinta.

Los CU o Computer Unit es como los define AMD. Cuando se vió el diagrama oficial de Microsoft, y vieron los 12 SC

dijeron que no eran mas que los CU pero Microsoft los había cambiado el nombre y se llamaban Shader Cores o SC pero eran lo mismo..

Sin embargo, en esta diapositiva, también oficial de Microsoft, vemos que no los llama SC si no CU (Computer Units) ¿pero no eran SC? (Shader Cores) ¿entonces por qué pone "six computer units" + "six computer units"? M$ tan tonta eres que encima de que te gastas un pastón en cambiarle el nombre vas y te confundes??

Bueno, aquí podéis ver lo que digo..

O igual no se han confundido y es una especie de 12 SC + 12 CU?

Nuhar escribió:Desde el total desconocimiento, los shader compute puede ser un determinado proceso que toma el CU?

radeonxt escribió:Lo que me extraña es que no presenten nada a estas alturas, o tienen demasiada paciencia, o están demasiado seguros de que va a ser un bombazo o no se que... por que no tiene sentido viendo como van las ventas no empezar a sacar cartas a la mesa...

Si la consola tuviese el 75% de las ventas de su rival, pues aún iría confiado, pero es que no es el caso... y si el consumidor valora la potencia de la máquina, pues ya que a nivel teórico no es más potente, al menos demostrar que se puede aprovechar mucho mejor y dar mejores resultados o iguales que su rival con menos potencia teórica...

no entiendo nada...

Nuhar escribió:Desde el total desconocimiento, los shader compute puede ser un determinado proceso que toma el CU?

radeonxt escribió:Lo que me extraña es que no presenten nada a estas alturas, o tienen demasiada paciencia, o están demasiado seguros de que va a ser un bombazo o no se que... por que no tiene sentido viendo como van las ventas no empezar a sacar cartas a la mesa...

Si la consola tuviese el 75% de las ventas de su rival, pues aún iría confiado, pero es que no es el caso... y si el consumidor valora la potencia de la máquina, pues ya que a nivel teórico no es más potente, al menos demostrar que se puede aprovechar mucho mejor y dar mejores resultados o iguales que su rival con menos potencia teórica...

no entiendo nada...

argam escribió:Realmente no entiendia que Microsoft no hablase del potencial de su consola (asumiendo que esta ahi pero escondido), sobre todo viendo las ventas. Pero pensandolo un poco me da que seria contraproducente decir: "tenemos una consola con una arquitectura avanzada, pero el sw que la acompanya esta en panyales", porque los consumidores podrian interpretar el mensaje como "hemos lanzado una consola a medio terminar" o "hemos hecho un lanzamiento un poco chapuza".

Ante ese riesgo mejor callar y seguir trabajando (lo que me parece la mejor estrategia).

En cuanto a hasta donde llegara el potencial de one, yo no soy tan optimista como muchos por aqui. Me conformaria con que los multi estuvieran 100% parejos en el futuro.

Un saludo!

![brindis [beer]](/images/smilies/nuevos2/brindando.gif)

colets escribió:Pues si se me permite la opinión, creo que Microsoft llama Compute Unit o Shader Core al mismo componente. En la frase remarcado en rojo de la derecha, dice algo como

Cada CU [sigue explicando como se reparten las instrucciones en el CU].Para más información, ver el whitepaper "Xbox One GPU Shader Cores". Documento que seguro que tiene bastante miga...

Desconozco porqué usar una nomenclatura u otra (¿puede ser según la tarea que vaya a realizar? )

En cuanto a lo de la memoria no tengo muy claro, se supone que cada CU o SC tiene 16Kb de L1 y 64KB de lo que AMD llama Local Data Share, pero en el diagrama se que están colocadas fuera de los SCs (¿quizá para que se vea bien en el diagrama?) y luego una memoria L2 de 512 KB y otra GSM ¿? de 64KB, que parece común a toda la GPU.

Por cierto, en la parte de la izquierda describe cada uno de los 4 SIMD (lo que AMD en su esquema marca como vector unit). Y porqué debería ser considerado como una unidad vectorial en el sentido que acepta un vector de hilos, y que si se considera por hilo es una unidad escalar (aquí supongo que es porque en cada ciclo una ALU ejecuta una operación del hilo que le toca).

Con esa información a quien le apetezca contar rayitas de la famosa imagen de las ALUs puede tener nuevo entretenimiento.

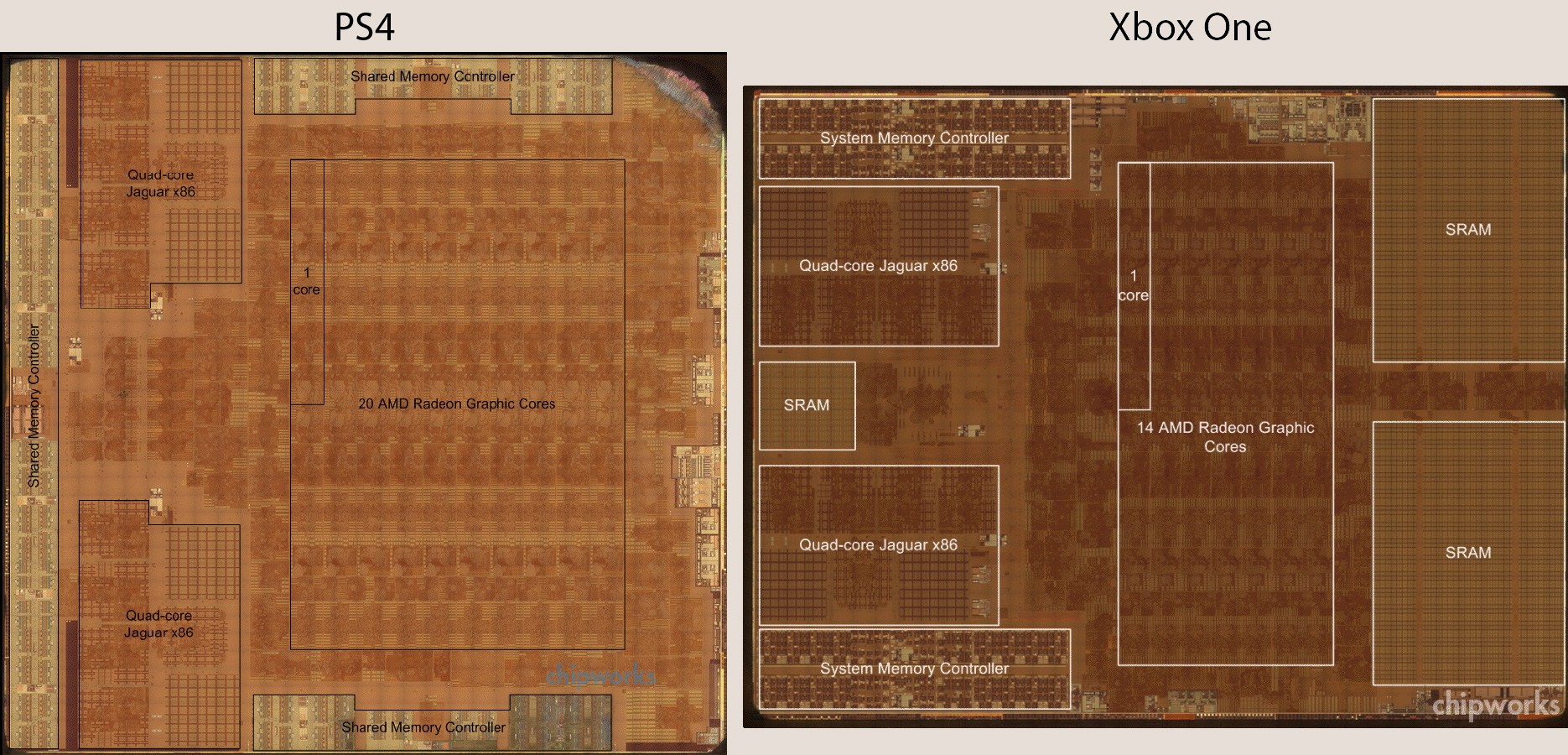

Siempre he creído que contar rayita por ALU partía de un error de base: se tomaba ese trozo como un CU completo(Compute Unit, Shader Core, Graphic Core o como se le llame), cuando viendo la imagen de chipworks parece alrededor de 1/5 de un CU.

Para mi tendría más sentido que ese recorte sea uno de los cuatro SIMDs (o Vector Unit según el esquema de AMD) de cada CU, también podría ser la memoria L1 del CU o la parte de las "texture filter units". Si es un VU, esasa rayitas deberían ser: 16 ALUs, 256 registros vectoriales, 512 registros escalares y no tengo muy claro si ahí también se vería parte del planificador.

Aquí es donde sí veo una diferencia con el esquema de GCN que se ha puesto páginas atrás. Mientras que AMD solo habla de registros vectoriales (4x64 KB) en cada SIMD, Microsoft habla de esos registros vectoriales (256) y de que también hay registros escalares (512).

Szasz escribió:Si es lo mismo SC q CU. ¿Como explicarías lo de la L2?

L2 SC 512KB - 32 way (4x8)

L2 CU 512KB - 16 way

![risa con gafas [chulito]](/images/smilies/nuevos/sonrisa_ani2.gif)

Chifrinillo escribió:Szasz escribió:Si es lo mismo SC q CU. ¿Como explicarías lo de la L2?

L2 SC 512KB - 32 way (4x8)

L2 CU 512KB - 16 way

Tiene pinta de que están en en mismo espacio físico pero no son lo mismo.

Es decir, se aprovechan las mismas ALUS pero de una manera diferente... Desdoblamiento

papatuelo escribió:Guau!!! Era imposible de imaginar, quien lo habría dicho!!!

![otra sonrisa [jaja]](/images/smilies/nuevos2/otrasonrisa.gif)

Szasz escribió:colets escribió:Pues si se me permite la opinión, creo que Microsoft llama Compute Unit o Shader Core al mismo componente. En la frase remarcado en rojo de la derecha, dice algo como

Cada CU [sigue explicando como se reparten las instrucciones en el CU].Para más información, ver el whitepaper "Xbox One GPU Shader Cores". Documento que seguro que tiene bastante miga...

Desconozco porqué usar una nomenclatura u otra (¿puede ser según la tarea que vaya a realizar? )

En cuanto a lo de la memoria no tengo muy claro, se supone que cada CU o SC tiene 16Kb de L1 y 64KB de lo que AMD llama Local Data Share, pero en el diagrama se que están colocadas fuera de los SCs (¿quizá para que se vea bien en el diagrama?) y luego una memoria L2 de 512 KB y otra GSM ¿? de 64KB, que parece común a toda la GPU.

Por cierto, en la parte de la izquierda describe cada uno de los 4 SIMD (lo que AMD en su esquema marca como vector unit). Y porqué debería ser considerado como una unidad vectorial en el sentido que acepta un vector de hilos, y que si se considera por hilo es una unidad escalar (aquí supongo que es porque en cada ciclo una ALU ejecuta una operación del hilo que le toca).

Con esa información a quien le apetezca contar rayitas de la famosa imagen de las ALUs puede tener nuevo entretenimiento.

Siempre he creído que contar rayita por ALU partía de un error de base: se tomaba ese trozo como un CU completo(Compute Unit, Shader Core, Graphic Core o como se le llame), cuando viendo la imagen de chipworks parece alrededor de 1/5 de un CU.

Para mi tendría más sentido que ese recorte sea uno de los cuatro SIMDs (o Vector Unit según el esquema de AMD) de cada CU, también podría ser la memoria L1 del CU o la parte de las "texture filter units". Si es un VU, esasa rayitas deberían ser: 16 ALUs, 256 registros vectoriales, 512 registros escalares y no tengo muy claro si ahí también se vería parte del planificador.

Aquí es donde sí veo una diferencia con el esquema de GCN que se ha puesto páginas atrás. Mientras que AMD solo habla de registros vectoriales (4x64 KB) en cada SIMD, Microsoft habla de esos registros vectoriales (256) y de que también hay registros escalares (512).

Si es lo mismo SC q CU. ¿Como explicarías lo de la L2?

L2 SC 512KB - 32 way (4x8)

L2 CU 512KB - 16 way

colets escribió:Szasz escribió:colets escribió:Pues si se me permite la opinión, creo que Microsoft llama Compute Unit o Shader Core al mismo componente. En la frase remarcado en rojo de la derecha, dice algo como

Cada CU [sigue explicando como se reparten las instrucciones en el CU].Para más información, ver el whitepaper "Xbox One GPU Shader Cores". Documento que seguro que tiene bastante miga...

Desconozco porqué usar una nomenclatura u otra (¿puede ser según la tarea que vaya a realizar? )

En cuanto a lo de la memoria no tengo muy claro, se supone que cada CU o SC tiene 16Kb de L1 y 64KB de lo que AMD llama Local Data Share, pero en el diagrama se que están colocadas fuera de los SCs (¿quizá para que se vea bien en el diagrama?) y luego una memoria L2 de 512 KB y otra GSM ¿? de 64KB, que parece común a toda la GPU.

Por cierto, en la parte de la izquierda describe cada uno de los 4 SIMD (lo que AMD en su esquema marca como vector unit). Y porqué debería ser considerado como una unidad vectorial en el sentido que acepta un vector de hilos, y que si se considera por hilo es una unidad escalar (aquí supongo que es porque en cada ciclo una ALU ejecuta una operación del hilo que le toca).

Con esa información a quien le apetezca contar rayitas de la famosa imagen de las ALUs puede tener nuevo entretenimiento.

Siempre he creído que contar rayita por ALU partía de un error de base: se tomaba ese trozo como un CU completo(Compute Unit, Shader Core, Graphic Core o como se le llame), cuando viendo la imagen de chipworks parece alrededor de 1/5 de un CU.

Para mi tendría más sentido que ese recorte sea uno de los cuatro SIMDs (o Vector Unit según el esquema de AMD) de cada CU, también podría ser la memoria L1 del CU o la parte de las "texture filter units". Si es un VU, esasa rayitas deberían ser: 16 ALUs, 256 registros vectoriales, 512 registros escalares y no tengo muy claro si ahí también se vería parte del planificador.

Aquí es donde sí veo una diferencia con el esquema de GCN que se ha puesto páginas atrás. Mientras que AMD solo habla de registros vectoriales (4x64 KB) en cada SIMD, Microsoft habla de esos registros vectoriales (256) y de que también hay registros escalares (512).

Si es lo mismo SC q CU. ¿Como explicarías lo de la L2?

L2 SC 512KB - 32 way (4x8)

L2 CU 512KB - 16 way

Pues ahí me pillas, la verdad. No he visto de donde ha salido eso, me lo he debido saltar. ¿Me puedes referenciar donde está escrito esas dos frases?

La L2 (en teoría) es común para todos los SC.

Y sí, me refería a ese gif, lo más lógico es que esa es la parte del principio (o del final, según se mire) de 7 SCs. Lo marcado en rojo es imposible en mi opinión que sean solo ALUs.

colets escribió:ok, porque he buscado y no lo encuentro.

Por cierto, buscando en el hilo y releyendo el artículo de VGLeaks, esa parte de la documentación lleva igual desde enero del 2013, me refiero a donde habla del SIMD, scheduler,etc es el mismo texto que en el artículo de VGleaks. No digo que tenga que ser, perooo ¿no podría ser que haya partes de la documentación que se han escrito (o han tenido una edición) más tarde?

papatuelo, si no niego que visualmente haya diferencias. Lo que digo es que de esa imagen es imposible decir que eso son las ALUs, y de ahí extrapolar el número de ALUs (si fuera así, habría que multiplicar por cuatro el número obtenido de ALUs). Tendría más sentido (bueno, sigo diciendo que más bien poco) haberlo hecho a partir de un recorte de un solo CU. Partiendo de la imagen de chipworks sería en vertical en vez de en horizontal como la que has puesto.

¿Alguien sabe de algún sitio donde esté la litografía con una resolución decente?

colets escribió:Vale, gracias por el enlace. Es la imagen del artículo de chipworks, que la verdad, tampoco es que tenga mucha resolución:

http://www.chipworks.com/en/technical-c ... -xbox-one/

Haciendo un photoshop guarrro, solo de la parte de la GPU:

El rectángulo blanco que marca chipworks como "graphics core", sí veo sentido que sea unos de los 14 que aquí llamamos Shader Core o Compute Unit, o por decidir que sean dos cosas diferentes, que, en mi opinión, no es así.

El rectángulo verde es la base de tu gif y el recuadrillo rojo con una S es de donde se ha sacado lo del número de ALUs, el que está en rojo en tu gif.

Sabemos que las ALUs están dentro de los SIMDs y que hay cuatro SIMDs por cada Shader Core, debería haber cuatro bloques de esos rojos en cada Shader Core.

He copiado y puesto cuatro rectángulos de esos rojos con la S al lado del "graphics core" donde más o menos deberían ir, aunque a saber si no estoy metiendo ahí la pata hasta el fondo.

Para ser sincero la imagen no permite disntiguir mucho, pero sí tiene pinta de que el cuadrado rojo de tu gif es uno de los cuatro SIMDs, y en ese caso lo que se ve ahí no son solo ALUs, serían ALUs + registros por lo menos. Por eso, el argumento de que ahí tiene que ver más ALUs porque se ven más rayitas (dentro del cuadrado rojo) no me convence.

Más que por el aspecto, que puede ser por diferente disposición, encapsulado, o sencillamente, porque de lo que estamos discutiendo no son las ALUs; si cada SIMD tuviera 32 ALUs en vez de las 16 esperables cada SIMD debería ocupar mucha mayor área y un Graphic Core de Xbox One sería mucho más grande que uno de Sea Islands normal. Porque creo que están confirmado que están hechos por el mismo fabricante (AMD), en la misma planta (TSMC) y con la misma tecnología (28nm).

Sigo sin ver nada que me indique que el número de ALUs es de más de 768. Ojo, y sé que toda la parrafada que he puesto tampoco demuestra que no sea así. Pero la lógica,las cifras dadas por AMD, Microsoft y ciertos artículos, me dicen que es casi seguro que haya 768 ALUs operativas.

According to example, three types of engines are shown: 1) general graphics engine (GFX) (354(1), 354(2)) for texture fetch, matrix multiply and possibly pixel operations; 2) a scan line engine (GFX SC) (354(3)), which performs scan line conversion and 3) a move engine (354(4)) which reduces the bandwidth pressure on the L1 caches by moving data within a shared L2$

papatuelo escribió:According to example, three types of engines are shown: 1) general graphics engine (GFX) (354(1), 354(2)) for texture fetch, matrix multiply and possibly pixel operations; 2) a scan line engine (GFX SC) (354(3)), which performs scan line conversion and 3) a move engine (354(4)) which reduces the bandwidth pressure on the L1 caches by moving data within a shared L2$

![risa con gafas [chulito]](/images/smilies/nuevos/sonrisa_ani2.gif)

![risita [risita]](/images/smilies/nuevos/sonrisa_ani1.gif)

Scanline rendering is an algorithm for visible surface determination, in 3D computer graphics, that works on a row-by-row basis rather than a polygon-by-polygon or pixel-by-pixel basis. All of the polygons to be rendered are first sorted by the top y coordinate at which they first appear, then each row or scanline of the image is computed using the intersection of a scanline with the polygons on the front of the sorted list, while the sorted list is updated to discard no-longer-visible polygons as the active scan line is advanced down the picture.

papatuelo escribió:Una preguntilla, ?Qué significa TCC y TCP?

Todo lo que encuentro al respecto no tiene sentido

Edito:

Creo que ya lo se:

Transactional conherence and consistency:

-Similar to prior thread-level speculation (TLS) techniques

*CMU Stampede

*Stanford Hydra

*Wisconsin Multiscalar

*UIUC speculative multithreading CMP

-Loosely coupled TLS system

-Completely eliminates conventional cache coherence and consistency models

-No MESI-style cache coherence protocol

-But require new hardware support

¿Puede ser?

Now another one from X.D.K

=========================

a definitive multilane (multi GPU)

uint __XB_GetLaneID ();

uint __XB_GetCUID ();

uint __XB_GetWaveID ();

uint __XB_GetSIMDID ();

uint __XB_GetSEID ();

Lane ID WOW!!!,

That X.D.K explain every thread will have those above ID

on normal GPU there is no LaneID !!!

there is only CUID !!! , indicating the thread reside in which CU number !!

Chifrinillo escribió:Now another one from X.D.K

=========================

a definitive multilane (multi GPU)

uint __XB_GetLaneID ();

uint __XB_GetCUID ();

uint __XB_GetWaveID ();

uint __XB_GetSIMDID ();

uint __XB_GetSEID ();

Lane ID WOW!!!,

That X.D.K explain every thread will have those above ID

on normal GPU there is no LaneID !!!

there is only CUID !!! , indicating the thread reside in which CU number !!

¿Es eso cierto?

¿Es la prueba definitiva de el MULTI-GPU?